# **KIOXIA** microSDHC Card Specification

This document is subjected to change without any notice. In developing your designs, please ensure that KIOXIA products are used within specified the latest version or information.

Contact for Technical Information: Memory Application Engineering Dept. Memory Division KIOXIA Corporation

### **IMPORTANT NOTICE**

- No parts of this document may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electric, photocopying, recording or otherwise, without permission of KIOXIA.

- Implementation of the cryptographic functions used in the SD card may be subject to export control by the United States, Japanese and/or other governments.

- KIOXIA does not make any warranty, express or implied, with respect to this document, including as to licensing, Non-infringement, merchantability or fitness for a particular purpose.

# Application

This document describes the specifications of the KIOXIA Standard microSDHC Card. To commence the design of the host system for microSDHC Card, please refer the "9.Host Interface design notes". The descriptions of microSD in this document may be read as microSDHC fitly.

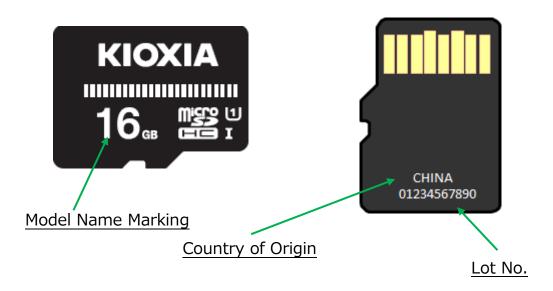

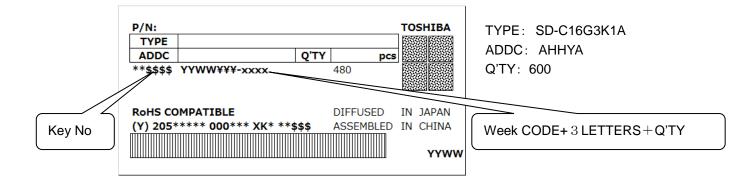

# 1. Production Code

KIOXIA Standard microSDHC Card: Capacity Model Name

microSDHC

16GB SD-C16G3K1A (AHHYA)

# 2. Product Overview

The microSD Card is a Memory Card of Small and Thin with Flash Memory.

# 3. SD Card Features

### Table1: SD card Features

| Design                | KIOXIA Standard (Fig.1)                                                                                                        |               |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|--|

| Contents              | None (OEM Design Available)                                                                                                    | ID Programmed |  |  |  |  |  |

| Security Functions    | ctions SD Security Specification Ver.4.00 Compliant (Non-CPRM)<br>*CPRM: Contents Protection for Recording Media Specification |               |  |  |  |  |  |

| Logical Format        | SD File System Specification Ver.3.00 Compliant<br>( DOS-FAT Based formatted )                                                 |               |  |  |  |  |  |

| Physical , Electrical |                                                                                                                                |               |  |  |  |  |  |

| Electrical            | Operating Voltage: 2.7V to 3.6 V (Memory Operation)                                                                            |               |  |  |  |  |  |

|                       | Interfaces: SD Card Interface, (SD : 4 or 1bit)                                                                                |               |  |  |  |  |  |

|                       | SPI Mode Compatible                                                                                                            |               |  |  |  |  |  |

|                       | SD Physical Layer Specification Ver.6.10 Compliant                                                                             |               |  |  |  |  |  |

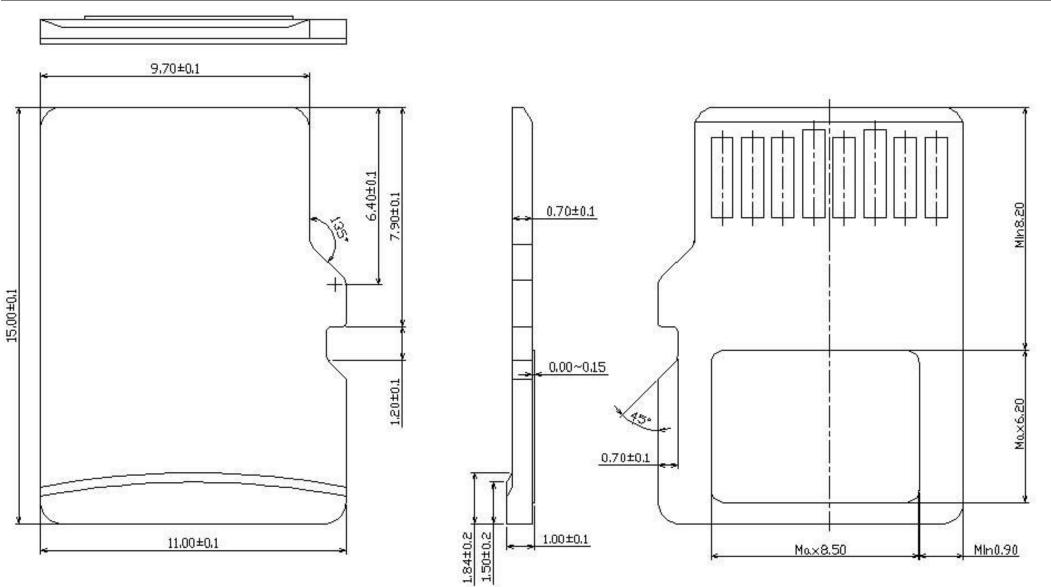

| Physical              | L: 15, W: 11, T: 1.0 (mm), Weight: 0.3g (typ.)                                                                                 |               |  |  |  |  |  |

|                       | microSD Card Addendum Ver.4.20 Compliant                                                                                       |               |  |  |  |  |  |

|                       | (Detailed Dimensions attached : sheet . 1)                                                                                     |               |  |  |  |  |  |

| Durability            | SD Physical Layer Specification Ver.6.10 Compliant                                                                             |               |  |  |  |  |  |

|                       | microSD Card Addendum Ver.4.20 Compliant                                                                                       |               |  |  |  |  |  |

| RoHS                  | The product(s) is/are compatible with RoHS regulations (EU directive                                                           |               |  |  |  |  |  |

|                       | 2011 / 65 / EU) as indicated, if any, on the packaging label ("[[G]]/RoHS                                                      |               |  |  |  |  |  |

|                       | COMPATIBLE", "[[G]]/RoHS[[Chemical symbol(s) of controlled                                                                     |               |  |  |  |  |  |

|                       | substance(s)]]", "RoHS COMPATIBLE" or "RoHS COMPATIBLE,                                                                        |               |  |  |  |  |  |

|                       | [[Chemical symbol(s) of controlled substance(s)]]>MCV"),                                                                       |               |  |  |  |  |  |

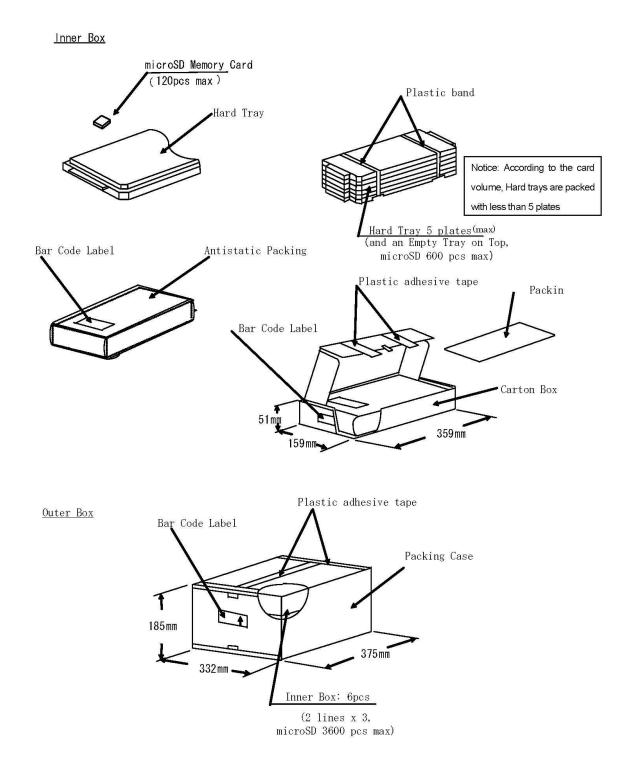

| Packaging             | Appendix5-1,Appendix5-2                                                                                                        |               |  |  |  |  |  |

### 3.1. MOLD

1) MoldMaterial: Epoxy Resin+Silicon DioxideFlameproof Grade: V-0(UL94)Heatproof Temperature: approx.400 degrees

# 4. Compatibility

### **Compliant Specifications**

- SD Memory Card Specifications

- Compliant with PHYSICAL LAYER SPECIFICATION Ver.6.10. (Part1)

- Compliant with FILE SYSTEM SPECIFICATION Ver.3.00. (Part2)

- Compliant with SECURITY SPECIFICATION Ver.4.00. (Part3)

- microSD Card Addendum Ver.4.20

Supplementary Explanation are described in "8. Others: Limited Conditions, SD Specification Compliance" in this document.

# **5. Physical Characteristics**

### 5.1. Temperature

- 1) Operation Conditions Temperature Range: Ta = -25 to +85 degrees centigrade

- 2) Storage Conditions Temperature Range: Tstg = -40 to +85 degrees centigrade

## 5.2. Moisture (Reliability)

- 1) Operation Conditions Temperature 25 degrees centigrade / 95% rel. humidity

- 2) Storage Conditions

- Temperature 40 degrees centigrade / 93% rel. humidity / 500h

### **5.3. Physical Characteristics**

### 1) Hot Insertion or Removal

KIOXIA microSD Card can remove or insert without power off the host system described in the 6.1 of the PHYSICAL LAYER SPECIFICATION. The connector to realize the Hot Insertion or Removal is defined in the 6.2 of the PHYSICAL LAYER SPECIFICATION.

### 2) Mechanical Write Protect Switch

microSD memory Card has no mechanical write protect switch.

# 6. Electrical Interface outlines

### 6.1. microSD Card Pins

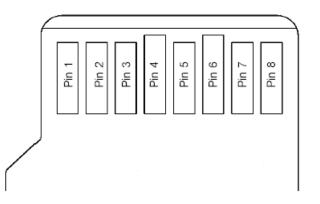

Table 2 describes the pin assignment of the microSD card. Fig.3 describes the pin assignment of the microSD card.

Please refer the detail descriptions by SD Card Physical Layer Specification.

Fig 3: microSD Card Pin assignment (Back view of the Card)

| Pins  | SD Mode         |           |                       |                 | SF     | PI Mode                |  |  |

|-------|-----------------|-----------|-----------------------|-----------------|--------|------------------------|--|--|

| FIIIS | Name            | IO type 1 | Description           | Name            | Ю Туре | Description            |  |  |

| 1     | DAT2            | I/O /PP   | Data Line[Bit2]       | RSV             |        |                        |  |  |

| 2     | CD/             | I/O/PP    | Card Detect / Data    | CS              | I      | Chip Select (neg true) |  |  |

|       | DAT3            |           | Line[Bit3]            |                 |        |                        |  |  |

| 3     | CMD             | PP        | Command/Response      | DI              |        | Data In                |  |  |

| 4     | $V_{dd}$        | S         | Supply Voltage        | V <sub>dd</sub> | S      | Supply Voltage         |  |  |

| 5     | CLK             | I         | Clock                 | SCLK            |        | Clock                  |  |  |

| 6     | V <sub>SS</sub> | S         | Supply voltage ground | V <sub>SS</sub> | S      | Supply voltage ground  |  |  |

| 7     | DAT0            | I/O /PP   | Data Line[Bit0]       | DO              | O/PP   | Data Out               |  |  |

| 8     | DAT1            | I/O /PP   | Data Line[Bit1]       | RSV             | -      | Reserved (*)           |  |  |

Table 2: microSD card pin assignment

1) S: Power Supply, I: Input, O: Output, I/O: Bi-directionally, 'PP' - IO using push-pull drivers (\*) These signals should be pulled up by host side with 10-100k ohm resistance in the SPI Mode.

Do not use NC pins.

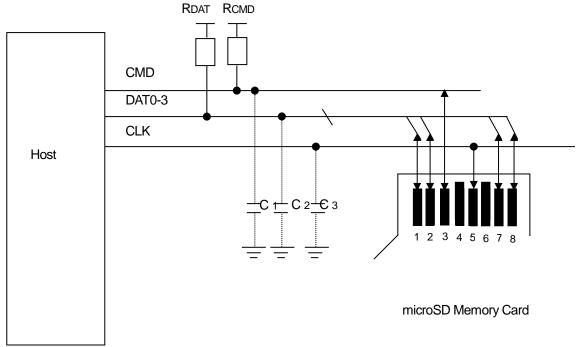

### 6.2 microSD Card Bus Topology

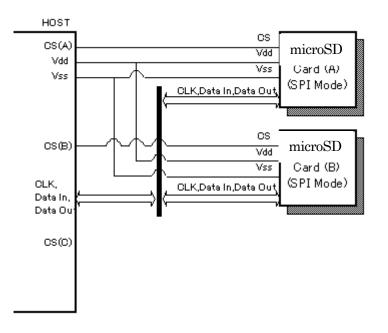

The microSD Memory Card supports two alternative communication protocols: SD and SPI Bus Mode.

Host System can choose either one of modes. Same Data of the microSD Card can read and write by both modes.

SD Mode allows the 4-bit high performance data transfer. SPI Mode allows easy and common interface for SPI channel. The disadvantage of this mode is loss of performance, relatively to the SD mode.

### 6.2.1 SD Bus Mode protocol

The SD bus allows the dynamic configuration of the number of data line from 1 to 4 Bi-directional data signal. After power up by default, the microSD card will use only DATO. After initialization, host can change the bus width.

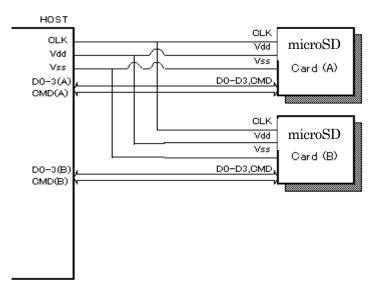

Multiplied microSD cards connections are available to the host. Common  $V_{dd}$ ,  $V_{ss}$  and CLK signal connections are available in the multiple connection. However, Command, Respond and Data lined (DAT0-DAT3) shall be divided for each card from host.

This feature allows easy tradeoff between hardware cost and system performance. Communication over the microSD bus is based on command and data bit stream initiated by a start bit and terminated by stop bit.

Command:

Commands are transferred serially on the CMD line. A command is a token to starts an operation from host to the card. Commands are sent to a addressed single card (addressed Command) or to all connected cards (Broad cast command).

#### Response:

Responses are transferred serially on the CMD line.

A response is a token to answer to a previous received command. Responses are sent from a addressed single card or from all connected cards.

#### Data:

Data can be transfer from the card to the host or vice versa. Data is transferred via the data lines.

Fig 4: microSD Card (SD Mode) connection Diagram

| CLK             | : Host card Clock signal                  |

|-----------------|-------------------------------------------|

| CMD             | : Bi-directional Command/ Response Signal |

| DAT0 - DAT3     | : 4 Bi-directional data signal            |

| V <sub>dd</sub> | : Power supply                            |

| Vss             | : GND                                     |

|                 |                                           |

### SD-C16G3K1A(AHHYA)

#### Table 3: SD Mode Command Set (+: Implemented, -: Not Implemented)

| CMD         Abbreviation         Impleme<br>nation         Note           CMD0         GO_IDLE_STATE         +         -           CMD2         ALL_SEND_CID         +         -           CMD3         SEND_RELATIVE_ADDR         +         -           CMD4         SET_DSR         -         DSR Register is not implemented.           CMD6         SWITCH_FUNC         +         -           CMD3         SEND_FCOND         +         -           CMD3         SEND_FCOND         +         -           CMD1         VOLTAGE_SWITCH         +         -           CMD11         VOLTAGE_SWITCH         +         -           CMD12         STOP_TRANSMISSION         +         -           CMD13         SEND_STATUS         +         -           CMD14         SEND_TATUS         +         -           CMD17         READ_MULTIPLE_BLOCK         +         -           CMD20         SPEED_CLASS_CONTROL         +         For SDHC/SDXC           CMD23         SET_BLOCK COUNT         +         -           CMD24         WRITE_BLOCK         +         -           CMD25         WRITE_NOT         -         Internal Write P                                        | (+: Implemented, -: Not Implemented) |                    |                    |                                              |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------|--------------------|----------------------------------------------|--|--|--|--|--|--|

| CMD2         ALL SEND_CID         +           CMD3         SEND_RELATIVE_ADDR         +           CMD4         SET_DSR         -         DSR Register is not implemented.           CMD6         SWITCH_FUNC         +            CMD7         SELECT/DESELECT_CARD         +           CMD8         SEND_CID         +           CMD10         SEND_CID         +           CMD11         VOLTAGE_SWITCH         +           CMD13         SEND_CID         +           CMD14         SETO_TRANSMISSION         +           CMD15         GO_INACTIVE_STATE         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_MUTPILE_BLOCK         +           CMD20         SPEED_CLASS_CONTROL         +           CMD21         SET_BLOCK COUNT         +           CMD23         SET_BLOCK COUNT         +           CMD24         WRTE_BLOCK         +           CMD25         WRTE_MUTPLE_BLOCK         +           CMD24         WRTE_PROT         -         Internal Write Protection is not implemented.           CMD23         SET_WRTE_PROT         -         Internal Write Protection is not implemented.                                     | CMD<br>Index                         | Abbreviation       | Impleme<br>ntation | Note                                         |  |  |  |  |  |  |

| CMD3         SEND RELATIVE ADDR         +           CMD4         SET DSR         -         DSR Register is not implemented.           CMD6         SWITCH FUNC         +           CMD7         SELECT/DESELECT CARD         +           CMD8         SEND JF COND         +           CMD9         SEND JF COND         +           CMD10         SEND JF COND         +           CMD11         VOLTAGE SWITCH         +           CMD12         STOP TRANSMISSION         +           CMD13         SEND STATUS         +           CMD15         GO_INACTIVE_STATE         +           CMD16         SET BLOCKLEN         +           CMD17         READ_SINGLE BLOCK         +           CMD20         SFED_CLASS CONTROL         +           CMD23         SET BLOCK CONT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_PROT         -           CMD26         WRITE_PROT         -           CMD27         PROGRAM_CSD         +           CMD28         SET_WRITE_PROT         -           CMD30         SEND_WITE PROT         -           Internal Write Protection is not imple                                                | CMD0                                 | GO_IDLE_STATE      | +                  |                                              |  |  |  |  |  |  |

| CMD4         SET_DSR         -         DSR Register is not implemented.           CMD6         SWITCH_FUNC         +           CMD7         SELECT/DESELECT_CARD         +           CMD8         SEND_CD         +           CMD10         SEND_CD         +           CMD10         SEND_CD         +           CMD11         VOLTAGE_SWITCH         +           CMD12         STOP_TRANSMISSION         +           CMD13         SEND_CSD         +           CMD14         SET_DCSC         +           CMD15         GO_INACTIVE_STATE         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_MULTIPLE_BLOCK         +           CMD20         SPEED_CLASS_CONTROL         +           CMD23         SET_BLOCK COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_BLOCK         +           CMD24         WRITE_PROT         -           CMD25         WRITE_PROT         -           CMD28         SET_WR_BLK_START         +           CMD30         SEND_WRITE_PROT         -         Internal Write Protection is not implemented.                                                              | CMD2                                 |                    | +                  |                                              |  |  |  |  |  |  |

| CMD4         SET_DSR         -         DSR Register is not implemented.           CMD6         SWITCH_FUNC         +           CMD7         SELECT/DESELECT_CARD         +           CMD8         SEND_CD         +           CMD10         SEND_CD         +           CMD10         SEND_CD         +           CMD11         VOLTAGE_SWITCH         +           CMD12         STOP_TRANSMISSION         +           CMD13         SEND_CSD         +           CMD14         SET_DCSC         +           CMD15         GO_INACTIVE_STATE         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_MULTIPLE_BLOCK         +           CMD20         SPEED_CLASS_CONTROL         +           CMD23         SET_BLOCK COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_BLOCK         +           CMD24         WRITE_PROT         -           CMD25         WRITE_PROT         -           CMD28         SET_WR_BLK_START         +           CMD30         SEND_WRITE_PROT         -         Internal Write Protection is not implemented.                                                              | CMD3                                 | SEND RELATIVE ADDR | +                  |                                              |  |  |  |  |  |  |

| CMD6         SWITCH FUNC         +           CMD7         SELECT/DESELECT_CARD         +           CMD8         SEND_IF_COND         +           CMD9         SEND_IF_COND         +           CMD10         SEND_CSD         +           CMD11         VOLTAGE_SWITCH         +           CMD13         SEND_STAVUS         +           CMD16         SEND_TRANSMISSION         +           CMD17         SEND_STATUS         +           CMD16         SEND_TATUS         +           CMD17         READ_SINGLE BLOCK         +           CMD18         READ_MULTIPLE BLOCK         +           CMD20         SPEED_CLASS CONTROL         +         For SDHC/SDXC           CMD21         SET_BLOCK COUNT         +         CMD22           CMD22         SET_MULTIPLE_BLOCK         +         CMD22           CMD23         SET_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD24         WRITE_BLOCK         +            CMD23         SET_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD24         SEND_WRITE_PROT         -         Internal Write Protection is not implemented.     < |                                      |                    | -                  | DSR Register is not implemented.             |  |  |  |  |  |  |

| CMD7         SELECT/DESELECT_CARD         +           CMD8         SEND_IF_COND         +           CMD10         SEND_CD         +           CMD11         VOLTAGE_SWITCH         +           CMD13         SEND_CSD         +           CMD14         SEND_CSD         +           CMD15         SEND_CSD         +           CMD16         SEND_CSD         +           CMD17         SEND_STATUS         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_MULTPLE_BLOCK         +           CMD20         SPEED_CLASS_CONTROL         +           CMD210         SET_BLOCK COUNT         +           CMD23         SET_BLOCK COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_MULTPLE_BLOCK         +           CMD24         WRITE_PROT         -         Internal Write Protection is not implemented.           CMD30         SEN_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD32         ERASE_WR_BLK_START         +            CMD33         ERASE_WR_BLK_START         +            CMD42                                                           |                                      |                    | +                  |                                              |  |  |  |  |  |  |

| CMD8         SEND_IF_COND         +           CMD9         SEND_CSD         +           CMD11         VOLTAGE_SWITCH         +           CMD12         STOP_TRANSMISSION         +           CMD13         SEND_STATUS         +           CMD14         SEND_STATUS         +           CMD15         GO_INACTIVE_STATE         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_SINGLE_BLOCK         +           CMD18         READ_MULTIPLE_BLOCK         +           CMD20         SPEED_CLASS_CONTROL         +         For SDHC/SDXC           CMD24         WRITE_BLOCK         +            CMD24         WRITE_BLOCK         +            CMD25         WRITE_ROCK         +            CMD26         WRITE_ROCK         +            CMD25         WRITE_PROT         -         Internal Write Protection is not implemented.           CMD29         CLR_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD32         ERASE_WR_BLK_END         +            CMD33         ERASE_WR_BLK_END         +           CMD42 <td< td=""><td></td><td></td><td></td><td></td></td<>                          |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD9         SEND_CSD         +           CMD10         SEND_CID         +           CMD11         VOLTAGE_SWITCH         +           CMD12         STOP_TRANSMISSION         +           CMD13         SEND_STATUS         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_SNGLE BLOCK         +           CMD18         READ_MULTIPLE_BLOCK         +           CMD20         SPEED_CLASS_CONTROL         +           CMD23         SET_BLOCK COUNT         +           CMD24         WRITE_BLOCK         +           CMD23         SET_BLOCK COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_MULTIPLE_BLOCK         +           CMD26         WRITE_MULTIPLE_BLOCK         +           CMD27         PROGRAM_CSD         +           CMD28         SET_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD30         SEND_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD33         ERASE_WR_BLK_END         +         -           CMD33         ERASE_WR_BLK_END         +         -                                  |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD10         SEND_CID         +           CMD11         VOLTAGE_SWITCH         +           CMD12         STOP_TRANSMISSION         +           CMD13         SEND_STATUS         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_SINGLE_BLOCK         +           CMD18         READ_MULTIPLE_BLOCK         +           CMD19         SEND_TUNING_PATTERN         +           CMD20         SPEED_CLASS_CONTROL         +           CMD218         SET BLOCK COUNT         +           CMD22         SET BLOCK COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_MULTIPLE_BLOCK         +           CMD26         WRITE_MULTIPLE_BLOCK         +           CMD27         PROGRAM_CSD         +           CMD28         SET_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD30         SEND_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD32         ERASE_WR_BLK_END         +         CMD33           CMD33         ERASE_WR_BLK_END         +         CMD42           CMD42         LOCK_UNLOCK         +            |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD11         VOLTÄGE SWITCH         +           CMD12         STOP_TRANSMISSION         +           CMD13         SEND STATUS         +           CMD15         GO_INACTIVE_STATE         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_SINGLE_BLOCK         +           CMD18         READ_MULTIPLE_BLOCK         +           CMD20         SETED_CLASS_CONTROL         +           CMD23         SET_BLOCK COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_MULTIPLE_BLOCK         +           CMD26         WRITE_MULTIPLE_BLOCK         +           CMD27         PROGRAM_CSD         +           CMD28         SET_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD30         SEND WRITE_PROT         -         Internal Write Protection is not implemented.           CMD312         ERASE_WR_BLK_END         +         -           CMD33         ERASE_WR_BLK_END         +         -           CMD34         ERASE_WR_BLK_END         +         -           CMD33         ERASE_WR_BLK_END         +         -           CMD42                       |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD12         STOP_TRANSMISSION         +           CMD13         SEND_STATUS         +           CMD15         GO_INACTIVE_STATE         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_MULTIPLE_BLOCK         +           CMD19         SEND_TUNING_PATTERN         +           CMD20         SPEED_CLASS_CONTROL         +           CMD23         SET BLOCK COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_MULTIPLE_BLOCK         +           CMD26         SET_WORK_COUNT         +           CMD27         PROGRAM_CSD         +           CMD28         SET_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD32         ERASE_WR_BLK_START         +            CMD33         ERASE_WR_BLK_END         +            CMD34         ERASE_WR_BLK_END         +            CMD33         ERASE_WR_BLK_END         +            CMD34         ERASE_WR_BLK_END         +            CMD35         APP_CMD         +            CMD42         LOCK_UNLOCK         +                                                                                          |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD13         SEND_STATUS         +           CMD15         GO_INACTIVE_STATE         +           CMD16         SET_BLOCKLEN         +           CMD17         READ_SINGLE_BLOCK         +           CMD18         READ_MULTIPLE_BLOCK         +           CMD20         SPEED_CLASS_CONTROL         +           CMD20         SPEED_CLASS_CONTROL         +           CMD23         SET_BLOCK_COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_NOCK_COUNT         +           CMD24         WRITE_BLOCK         +           CMD25         WRITE_PROT         -         Internal Write Protection is not implemented.           CMD20         SET_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD30         SEND_WRITE_PROT         -         Internal Write Protection is not implemented.           CMD31         ERASE_WR_BLK_START         +            CMD33         ERASE_WR_BLK_END         +           CMD42         LOCK_UNLOCK         +            CMD56         GEN_CMD         +            ACMD21         SD_APP_OP_OCOND         +                                             |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD15       GO_INACTIVE_STATE       +         CMD16       SET_BLOCKLEN       +         CMD17       READ_SINGLE_BLOCK       +         CMD18       READ_INULTIPLE_BLOCK       +         CMD20       SPEED_CLASS_CONTROL       +         CMD23       SET_BLOCK_COUNT       +         CMD24       WRITE_BLOCK       +         CMD25       WRITE_BLOCK       +         CMD26       WRITE_BLOCK       +         CMD27       WRITE_BLOCK       +         CMD28       SET_WRITE_PROT       -         CMD28       SET_WRITE_PROT       -         CMD29       CLR_WRITE_PROT       -         CMD30       SEND_WRITE_PROT       -         CMD31       ERASE_WR_BLK_START       +         CMD32       ERASE_WR_BLK_END       +         CMD33       ERASE_WR_BLK_END       +         CMD42       LOCK_UNLOCK       +         CMD55       APP_OMD       +         CMD56       GEN_CMD       -       This command is not specified.         ACMD21       SD_STATUS       +       -         ACMD22       SET_WR_BLK_ERASE_COUNT       +         ACMD43       SD_APP_OP_COND<                                                                                                                      |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD16       SET_BLOCKLEN       +         CMD17       READ_MULTIPLE_BLOCK       +         CMD18       READ_MULTIPLE_BLOCK       +         CMD20       SPEED_CLASS_CONTROL       +         CMD23       SET_BLOCK COUNT       +         CMD24       WRITE_BLOCK       +         CMD25       WRITE_MULTIPLE_BLOCK       +         CMD25       WRITE_MULTIPLE_BLOCK       +         CMD26       WRITE_PROT       -         CMD27       PROGRAM_CSD       +         CMD28       SET_WRITE_PROT       -         CMD30       SEND_WRITE_PROT       -         CMD31       SEND_WRITE_PROT       -         CMD32       ERASE_WR_BLK_START       +         CMD33       ERASE_WR_BLK_END       +         CMD34       ERASE       +         CMD42       LOCK_UNLOCK       +         CMD45       APP_CMD       -         CMD45       APP_CMD       +         CMD26       GEN_CMD       -         CMD45       APP_CMD       +         ACMD46       SET_BUS_WIDTH       +         ACMD20       SET WR_BLK_ERASE_COUNT       +         ACMD21 <td< td=""><td></td><td></td><td></td><td></td></td<>                                                                                                |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD17       READ_SINGLE_BLOCK       +         CMD18       READ_MULTIPLE_BLOCK       +         CMD20       SPEED_CLASS_CONTROL       +         CMD23       SET_BLOCK_COUNT       +         CMD24       WRITE_BLOCK       +         CMD25       WRITE_MULTIPLE_BLOCK       +         CMD26       WRITE_MULTIPLE_BLOCK       +         CMD27       PROGRAM_CSD       +         CMD28       SET_WRITE_PROT       -         CMD30       SEND_WRITE_PROT       -         CMD31       ERASE_WR_BLK_START       +         CMD32       ERASE_WR_BLK_START       +         CMD33       ERASE       +         CMD34       ERASE       +         CMD35       APP_CMD       +         CMD42       LOCK_UNLOCK       +         CMD55       APP_CMD       +         CMD55       APP_CMD       +         CMD13       SD_STATUS       +         ACMD23       SET_BUS_WIDTH       +         ACMD24       SEC_UR_ARD_ECKS       +         ACMD25       SET_UR_BLK_ERASE_COUNT       +         ACMD41       SD_APP_OP_OND       +         ACMD42 <td< td=""><td></td><td></td><td></td><td></td></td<>                                                                                                |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD18       READ_MULTIPLE_BLOCK       +         CMD19       SEND_TUNING_PATTERN       +         CMD20       SPEED_CLASS_CONTROL       +         CMD24       WRITE_BLOCK_COUNT       +         CMD25       WRITE_MULTIPLE_BLOCK       +         CMD26       WRITE_MULTIPLE_BLOCK       +         CMD27       PROGRAM_CSD       +         CMD28       SET_WRITE_PROT       -         CMD29       CLR_WRITE_PROT       -         CMD30       SEND_WRITE_PROT       -         CMD31       ERASE_WR_BLK_START       +         CMD33       ERASE_WR_BLK_END       +         CMD34       ERASE_MR_BLK_END       +         CMD35       APP_CMD       +         CMD34       ERASE_WR_BLK_END       +         CMD35       APP_CMD       +         CMD42       LOCK_UNLOCK       +         CMD56       GEN_CMD       -         ACMD4       SET_BUS_WIDTH       +         ACMD22       SEND_NUM_WR_BLOCKS       +         ACMD23       SET_WR_BLK_ERASE_COUNT       +         ACMD24       SECUR_CARD_DETECT       +         ACMD45       SECUR_CARD_DETECK       + <td></td> <td></td> <td></td> <td></td>                                                                                   |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD19       SEND_TUNING_PATTERN       +         CMD20       SPEED_CLASS_CONTROL       +         CMD23       SET_BLOCK       +         CMD24       WRITE_BLOCK       +         CMD25       WRITE_MULTIPLE_BLOCK       +         CMD26       WRITE_PROT       -         CMD29       CLR_WRITE_PROT       -         CMD30       SEND_WRITE_PROT       -         CMD31       SEASE_WR_BLK_START       +         CMD38       ERASE_WR_BLK_START       +         CMD38       ERASE_WR_BLK_START       +         CMD38       ERASE       +         CMD38       ERASE       +         CMD42       LOCK_UNLOCK       +         CMD56       GEN_CMD       +         CMD56       GEN_CMD       +         CMD23       SET_WR_BLK_ERASE_COUNT       +         ACMD23       SET_WR_BLK_ERASE_COUNT       +         ACMD23       SET_WR_BLK_ERASE_COUNT       +         ACMD24       SECURE_VRITE_MULTI_BLOCKS       +         ACMD25       SECURE_CARD_MULTI_BLOCK       -         ACMD26       SET_WR_BLK_ERASE_COUNT       +         ACMD26       SECURE_WRITE_MULTI_BLOCK                                                                                                                    |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD20       SPEED_CLASS_CONTROL       +       For SDHC/SDXC         CMD23       SET_BLOCK COUNT       +          CMD24       WRITE_BLOCK       +          CMD25       WRITE_MULTIPLE_BLOCK       +          CMD27       PROGRAM_CSD       +          CMD28       SET_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD29       CLR_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD31       SEND_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD32       ERASE_WR_BLK_START       +          CMD33       ERASE       +          CMD34       LOCK_UNLOCK       +          CMD42       LOCK_UNLOCK       +          CMD55       APP_CMD       +          CMD35       APP_CMD       +          ACMD6       SET_BUS_WIDTH       +          ACMD23       SEND_NUM_WR_BLOCKS       +          ACMD24       SET_CLR_CARD_DETECT       +          ACMD41       SEQURE_READ_MULTI_BLOCK       -          ACMD26                                                                                                                                                                      |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD23       SET_BLOCK_COUNT       +         CMD24       WRITE_BLOCK       +         CMD25       WRITE_MULTIPLE_BLOCK       +         CMD28       SET_WRITE_PROT       -         CMD29       CLR_WRITE_PROT       -         CMD30       SEND_WRITE_PROT       -         CMD31       SEND_WRITE_PROT       -         CMD32       ERASE_WR_BLK_START       +         CMD33       ERASE_WR_BLK_END       +         CMD38       ERASE_WR_BLK_END       +         CMD42       LOCK_UNLOCK       +         CMD55       APP_CMD       +         CMD56       GEN_CMD       +         CMD22       SET UNUN WR BLOCKS       +         ACMD23       SET_WR_BLK_ERASE_COUNT       +         ACMD41       SD_APP_OP_COND       +         ACMD42       SET_CLR_CARD_DETECT       +         ACMD41       SD_APP_OP_COND       +         ACMD42       SET_CLR_C                                                                                                                                                |                                      |                    |                    | For SDHC/SDXC                                |  |  |  |  |  |  |

| CMD24       WRITE_BLOCK       +         CMD25       WRITE_MULTIPLE_BLOCK       +         CMD27       PROGRAM_CSD       +         CMD28       SET_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD29       CLR_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD30       SEND_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD31       ERASE_WR_BLK_START       +       -         CMD32       ERASE_WR_BLK_END       +       -         CMD33       ERASE_WR_BLK_END       +       -         CMD34       ERASE       +       -         CMD35       APP_CMD       +       -         CMD55       APP_CMD       +       -         CMD54       SET_BUS_WIDTH       +       -         ACMD13       SD_STATUS       +       -         ACMD23       SET_WR_BLCKS       +       -         ACMD23       SET_WR_BLK_ERASE_COUNT       +       -         ACMD41       SD_APP_OP_COND       +       -         ACMD42       SET_CLR_CARD_DETECT       +       -         ACMD45       SECURE_WRITE_MULTI_BLOCK       - <td></td> <td></td> <td></td> <td></td>                               |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD25       WRITE_MULTIPLE_BLOCK       +         CMD27       PROGRAM_CSD       +         CMD28       SET_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD30       SEND_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD31       SEND_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD32       ERASE_WR_BLK_START       +         CMD33       ERASE_WR_BLK_END       +         CMD42       LOCK_UNLOCK       +         CMD55       APP_CMD       +         CMD56       GEN_CMD       -       This command is not specified.         ACMD6       SET_BUS_WIDTH       +          ACMD23       SET_WR_BLK_ERASE_COUNT       +          ACMD23       SET_UR_BLK_ERASE_COUNT       +          ACMD41       SD_APP_OP_COND       +          ACMD42       SET_CLR_CARD_DETECT       +          ACMD18       SECURE_READ_MULTI_BLOCK       -          ACMD43       SET_CLR_CARD_MULTI_BLOCK       -          ACMD43       SECURE_WRITE_MULT       -          ACMD45       SET_CER_RASE <td< td=""><td></td><td></td><td></td><td></td></td<>                                         |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD27PROGRAM_CSD+CMD28SET_WRITE_PROT-Internal Write Protection is not implemented.CMD30SEND_WRITE_PROT-Internal Write Protection is not implemented.CMD31ERASE_WR_BLK_START+CMD32ERASE_WR_BLK_END+CMD33ERASE_WR_BLK_END+CMD42LOCK_UNLOCK+CMD55APP_CMD+CMD56GEN_CMD-ACMD6SET_BUS_WIDTH+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD24SET_CR_CARD_DETECT+ACMD41SD_APP_OP_COND+ACMD51SEND_SCR+ACMD51SEND_SCR+ACMD26SECURE_RAD_MULTI_BLOCK-ACMD27SECURE_RAD_MULTI_BLOCK-ACMD48SECURE_RAND_MULTI_BLOCK-ACMD46SECURE_RAND_MULTI_BLOCK-ACMD26SECURE_RAND_MULTI_BLOCK-ACMD26SECURE_RAND_MULTI_BLOCK-ACMD43GET_MKB-ACMD44GET_MKB-ACMD45SET_CER_RASE-ACMD46SET_CER_RASE-ACMD47SET_CER_RN1-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD28       SET_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD29       CLR_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD30       SEND_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD31       ERASE_WR_BLK_START       +       -         CMD33       ERASE_WR_BLK_END       +       -         CMD34       ERASE_WR_BLK_END       +       -         CMD42       LOCK_UNLOCK       +       -         CMD55       APP_CMD       +       -         CMD56       GEN_CMD       -       This command is not specified.         ACMD2       SET_BUS_WIDTH       +       -         ACMD23       SET_WR_BLK_ERASE_COUNT       +       -         ACMD42       SET_UR_CARD_DETECT       +       -         ACMD41       SD_APP_OP_COND       +       -         ACMD42       SET_UR_CARD_MULTI_BLOCK       -       -         ACMD43       SECURE_READ_MULTI_BLOCK       -       -         ACMD45       SECURE_READ_MULTI_BLOCK       -       -         ACMD45       SECURE_MREM       -       -         ACMD45       SECURE_REASE       -<                                          |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD29       CLR_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD30       SEND_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD31       ERASE_WR_BLK_START       +         CMD33       ERASE_WR_BLK_END       +         CMD34       ERASE       +         CMD35       APP_CMD       +         CMD55       APP_CMD       +         CMD56       GEN_CMD       -         CMD58       JP_CMD       +         ACMD6       SET_BUS_WIDTH       +         ACMD23       SET_MUM_WR_BLOCKS       +         ACMD23       SET_WR_BLK_ERASE_COUNT       +         ACMD41       SD_APP_OP_COND       +         ACMD42       SET_CLR_CARD_DETECT       +         ACMD51       SEND_SCR       +         ACMD51       SECURE_READ_MULT_BLOCK       -         ACMD26       SECURE_WRITE_MULT_BLOCK       -         ACMD26       SECURE_READ       -         ACMD26       SECURE_REASE       -         ACMD43       GET_MKB       -         ACMD43       GET_MKB       -         ACMD43       GET_MKB       - <t< td=""><td></td><td></td><td>- <b>-</b></td><td>Internal Write Protection is not implemented</td></t<>          |                                      |                    | - <b>-</b>         | Internal Write Protection is not implemented |  |  |  |  |  |  |

| CMD30       SEND_WRITE_PROT       -       Internal Write Protection is not implemented.         CMD32       ERASE_WR_BLK_START       +         CMD33       ERASE_WR_BLK_END       +         CMD38       ERASE       +         CMD42       LOCK_UNLOCK       +         CMD55       APP_CMD       +         CMD56       GEN_CMD       -         ACMD6       SET_BUS_WIDTH       +         ACMD23       SET_WR_BLCKS       +         ACMD23       SET_WR_BLCCKS       +         ACMD23       SET_VR_BLK_ERASE_COUNT       +         ACMD41       SD_APP_OP_COND       +         ACMD42       SET_CLR_CARD_DETECT       +         ACMD51       SEND_SCR       +         ACMD25       SECURE_WRITE_MULTI_BLOCK       -         ACMD26       SECURE_READ_MULTI_BLOCK       -         ACMD26       SECURE_REN1       -         ACMD43       GET_MKB       -                                                                                                      |                                      |                    | -                  |                                              |  |  |  |  |  |  |

| CMD32ERASE_WR_BLK_START+CMD33ERASE_WR_BLK_END+CMD38ERASE+CMD42LOCK_UNLOCK+CMD55APP_CMD+CMD56GEN_CMD-ACMD6SET_BUS_WIDTH+ACMD13SD_STATUS+ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD41SD_APP_OP_COND+ACMD51SEND_SCR+ACMD53SECURE_READ_MULTI_BLOCK-ACMD54SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_READ_MULTI_BLOCK-ACMD26SECURE_READ_MULTI_BLOCK-ACMD43GET_MKB-ACMD44GET_MKB-ACMD43SET_CER_REASE-ACMD44SET_CER_RN1-ACMD45SET_CER_RN2-ACMD47SET_CER_RN2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |                    | -                  |                                              |  |  |  |  |  |  |

| CMD33ERASE_WR_BLK_END+CMD38ERASE+CMD42LOCK_UNLOCK+CMD55APP_CMD+CMD56GEN_CMD-ACMD6SET_BUS_WIDTH+ACMD13SD_STATUS+ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD25SECURE_READ_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD28SECURE_READ_MULTI_BLOCK-ACMD29SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD38SECURE_READ-ACMD44GET_MKB-ACMD45SET_CER_RN1-ACMD46SET_CER_RN1-ACMD47SET_CER_RS2-ACMD48SET_CER_RES2-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |                    | -                  |                                              |  |  |  |  |  |  |

| CMD38ERASE+CMD42LOCK_UNLOCK+CMD55APP_CMD+CMD56GEN_CMD-ACMD6SET_BUS_WIDTH+ACMD13SD_STATUS+ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD51SEND_SCR+ACMD51SEND_SCR+ACMD51SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD38SECURE_READ_MULTI_BLOCK-ACMD38SECURE_REASE-ACMD44GET_MKB-ACMD45SET_CER_RASE-ACMD46SET_CER_RN1-ACMD46SET_CER_RN1-ACMD48SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD42LOCK_UNLOCK+CMD55APP_CMD+CMD56GEN_CMD-This command is not specified.ACMD6SET_BUS_WIDTH+ACMD13SD_STATUS+ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD18SECURE_READ_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD27SECURE_READ_MULTI_BLOCK-ACMD43GET_MKB-ACMD44GET_MKB-ACMD45SET_CER_RASE-ACMD46SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD55APP_CMD+CMD56GEN_CMD-This command is not specified.ACMD6SET_BUS_WIDTH+ACMD13SD_STATUS+ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD25SECURE_READ_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD43GET_MKB-ACMD44GET_MKB-ACMD45SET_CER_RN2-ACMD46SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |                    |                    |                                              |  |  |  |  |  |  |

| CMD56GEN_CMD-This command is not specified.ACMD6SET_BUS_WIDTH+ACMD13SD_STATUS+ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD25SECURE_READ_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD38SECURE_WRITE_MKB-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD6SET_BUS_WIDTH+ACMD13SD_STATUS+ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD25SECURE_READ_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD38SECURE_WRITE_MULTI_BLOCK-ACMD43GET_MKB-ACMD44GET_MKB-ACMD45SET_CER_RASE-ACMD46SET_CER_RN1-ACMD47SET_CER_RS2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |                    |                    | This command is not aposified                |  |  |  |  |  |  |

| ACMD13SD_STATUS+ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD18SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MKB-ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |                    |                    | This command is not specified.               |  |  |  |  |  |  |

| ACMD22SEND_NUM_WR_BLOCKS+ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD18SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MULTI_BLOCK-ACMD38SECURE_WRITE_MKB-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RS2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD23SET_WR_BLK_ERASE_COUNT+ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD18SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MKB-ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD41SD_APP_OP_COND+ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD18SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MKB-ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD42SET_CLR_CARD_DETECT+ACMD51SEND_SCR+ACMD18SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MKB-ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MKB-ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD51SEND_SCR+ACMD18SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MKB-ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MKB+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |                    | -                  |                                              |  |  |  |  |  |  |

| ACMD18SECURE_READ_MULTI_BLOCK-ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MKB-ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD25SECURE_WRITE_MULTI_BLOCK-ACMD26SECURE_WRITE_MKB-ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      |                    | +                  |                                              |  |  |  |  |  |  |

| ACMD26SECURE_WRITE_MKB-ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |                    | -                  |                                              |  |  |  |  |  |  |

| ACMD38SECURE_ERASE-ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD43GET_MKB-ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD44GET_MID+ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | —                  |                    |                                              |  |  |  |  |  |  |

| ACMD45SET_CER_RN1-ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      | —                  |                    |                                              |  |  |  |  |  |  |

| ACMD46SET_CER_RN2-ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | —                  |                    |                                              |  |  |  |  |  |  |

| ACMD47SET_CER_RES2-ACMD48SET_CER_RES1-ACMD49CHANGE_SECURE_AREA-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD48     SET_CER_RES1     -       ACMD49     CHANGE_SECURE_AREA     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      |                    |                    |                                              |  |  |  |  |  |  |

| ACMD49 CHANGE_SECURE_AREA -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                      |                    |                    |                                              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |                    | -                  |                                              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |                    | -                  |                                              |  |  |  |  |  |  |

> CMD28, 29 and CMD30 are Optional Commands.

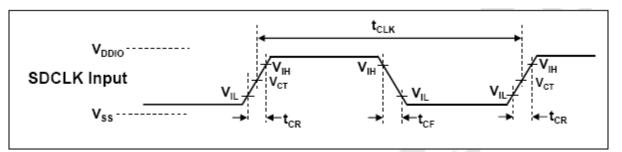

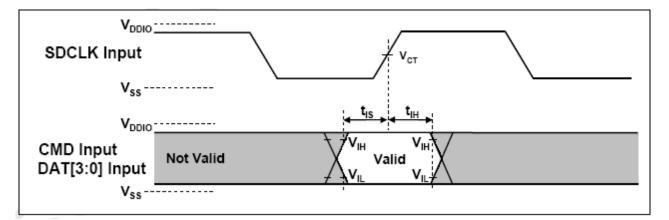

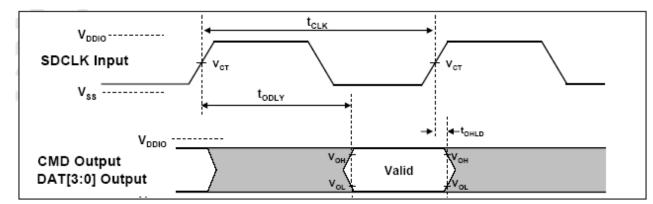

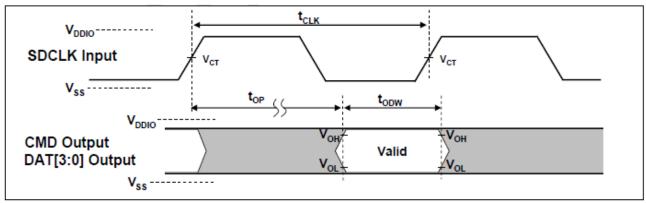

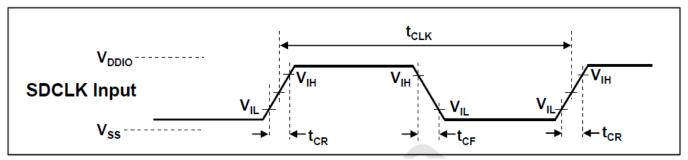

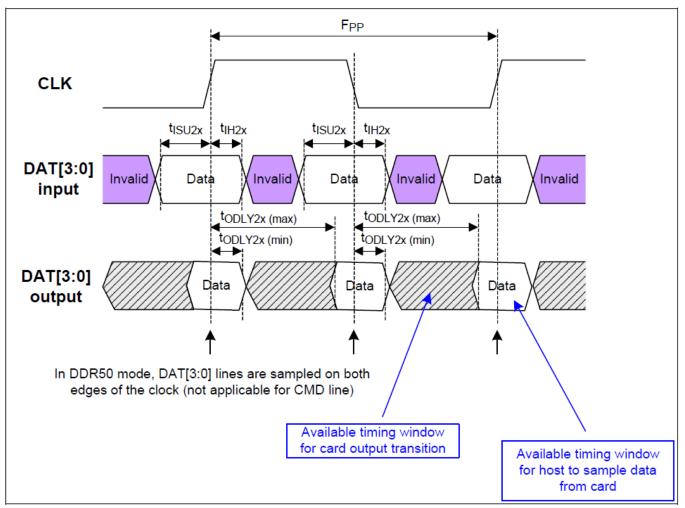

> CMD4 is not implemented because DSR register (Optional Register) is not implemented.